Cuprins

- 1. DATELE PENTRU PROIECTARE 2

- 2. DESCRIEREA CIRCUITELOR LOGICE PE BAZA TEHNOLOGIEI ECL 2

- 2.1. STRUCTURA UNEI PORȚI OR-NOR ECL 3

- 2.2. CARACTERISTICILE STATICE DE TRANSFER 3

- 2.3. AVANTAJELE ȘI DEZAVANTAJELE CIRCUITELOR LOGICE ECL 6

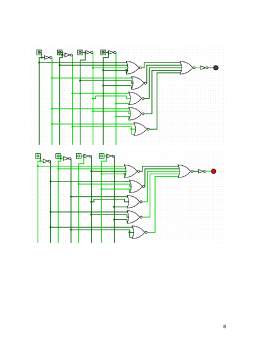

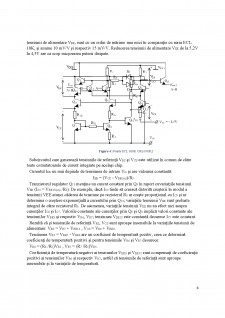

- 3. MINIMIZAREA FUNCȚIEI 7

- TABELUL DE ADEVĂR PENTRU FUNCȚIA PROPUSĂ 7

- TABELUL KARNAUGH 8

- TABELUL DE ADEVAR A FUNCȚIEI MINIMIZATE .8

- 4. SCHEMA LOGICĂ PENTRU FUNCȚIA MINIMIZATĂ 9

- 5. CALCULAREA PARAMETRILOR PORȚII FUNDAMENTALE ECL 10

- 5.1. CALCULAREA PARAMETRILOR STATICI 10

- 6. SCHEMA ELECTRICĂ A CIRCUITULUI PROPUS 13

- 7.Topologia elementelului logic ...14

- 7. CONCLUZIA 15

- BIBLIOGRAFIA 15

Extras din proiect

Datele pentru proiectare

Tensiunea de alimentare U,V -4,2

Factorul de asociere M 3

Coeficientul sortanță N 15

Factorul de amplificare al tranzistorului 29

Capacitatea sarcinii C_s ,pF 25

Puterea maximală consumată P_max,mW 55

U_in^(„0”)=U_out^(„0”)=U^(„0”),V -1.4

U_in^(„1”)=U_out^(„1”)=U^(„1”),V -0.75

Frecvența semnalului f_T,MHz 3000

Timpul de trecere t_int^(0>1),ns 5.6

Timpul de trecere t_int^(1>0),ns 4

Polaritatea logicii +

Setul logicii SAU-NU

Descrierea circuitelor logice pe baza tehnologiei ECL

Aceste circuite au apărut pe piață în 1964 și s-au dezvoltat în paralel cu circuitele TTL. Toate circuitele ECL au la bază comutatorul de curent realizat cu o pereche de tranzistoare “cuplate în emitor” după cum se arată în fig. 1.

Valorile rezistențelor R1, R2 și a sursei de curent constant IEE pot fi alese astfel încât tranzistoarele Q1, Q2 să nu se satureze; aceasta este una dintre justificările timpilor mici de propagare ai porților ECL (tp < 1ns).

Dacă tensiunea de intrare este gală cu tensiunea de referință, Vin = Vref, atunci tranzistoarele Q1, Q2 operează în RAN și IE1 = IE2 = IEE/2. Considerând βF - 100, rezultă IC1 = IC2 - IEE/2 iar tensiunile de la ieșirile circuitului au valorile Vout1 = - R1IEE/2 și respectiv Vout2 = - R2IEE/2. Modificarea tensiunii Vin cu numai ±100mV (Δ) față de valoarea de referință Vref determină ca aproape tot curentul IEE să treacă fie prin Q1 fie prin Q2, adică se realizează o comutare a curentului IEE între Q1 și Q2.

Tensiunile de ieșire corespunzătoare acestor două cazuri au valorile :

Vout1 = - R1IEE , Vout2 = 0 și respectiv Vout1 = 0, Vout2 = - R2IEE.

Structura unei porți OR-NOR ECL

Structura unei porți OR2-NOR2 din seria ECL 10K este reprezentată în fig.2. Sursa de curent IEE este obținută prin conectarea rezistorului R3 între comutatorul de curent (Q1, Q3, Q2) și sursa de tensiune VEE.

Figura 2: Poarta ECL 10K OR2-NOR2

Tranzistoarele Q5, Q6 (repetoare pe emitor) realizează deplasarea nivelului de tensiune la ieșiri cu 0,75V și asigură impedanțe de ieșire mici. Ieșirile complementare F1, F2 constituie surse de semnal pentru intrările altor porți ECL și sunt încărcate cu sarcini de tip R4, R5; pentru a se obține viteze mari de operare aceste ieșiri trebuie încărcate suplimentar cu rezistoare discrete, de obicei cu 2kΩ la -5,2V sau cu 50Ω la -2V.

Circuitul din fig.2 este prevăzut cu două conexiuni de masă, una pentru comutatorul de curent și tensiunea de referință (VCC1) iar cealaltă pentru repetoarele Q5, Q6 (VCC2). Conexiunea VCC1 are un potențial electric constant deoarece curentul prin comutatorul de curent este aproape constant; tensiunile de ieșire Vout1, Vout2 sunt definite în raport cu VCC1. Variațiile rapide ale curenților de sarcină, care circulă prin tranzistoarele Q5 și Q6, produc fluctuații de potențial pe conexiunea VCC2 însă acestea nu afecteză funcționarea subcircuitelor alimentate de la VCC1.

Două sau mai multe ieșiri ECL pot fi conectate împreună; funcția logică realizată prin această cablare este WOR (wired-OR).

Lăsarea în gol a unei intrări ECL este echivalentă cu aplicarea la acea intrare a unei tensiuni cu nivelul L; în ambele cazuri se blochează tranzistorul de intrare (Q1 sau Q3 în fig.2).

Bibliografie

1. Dumitru Secheianu. Microelectronica Editura militară București, 1988.

2. Maican S., ”Sisteme numerice cu circuite integrate” Ed. Tehnica, București 1980

3. Ștefan Gh., ”Circuite Integrate digitale”, Editura DENIX, București, 1993

4. Toacșe Gh., Nicula D. ”Electronică Digitală”, Editura Teora 2005

5. B.Wilkinson, ”Electronica digital”, Editura Teora, București, 2005

6. http://cadredidactice.ub.ro/rotardan/files/2012/04/electronica-digitala.pdf

7. http://ep.etc.tuiasi.ro/files/CID/porti_logice.pdf

8. http://shiva.pub.ro/new/wp-content/uploads/2014/10/MODUL-4bis-S-Tehnologii-de-realizare.-Parametrii-cracteristici.pdf

9. http://www.islavici.ro/cursuriold/Circuite%20integrate/05%20Familia%20ECL.pdf

10. https://ro.wikipedia.org/wiki/Familii_logice_comparate_de_circuite_integrate

11. Spânulescu I., Spânulescu S., ”Circuite Integrate Digitale și Sisteme cu Microprocesoare”, Editura Victor 2005

Preview document

Conținut arhivă zip

- Proiect de an ECL.docx