Extras din proiect

Tema :

1. Sa se implementeze un program in structura programabila de tip FFGA a unui program VHDL astfel incat sa se realizeze un numarator BCD.

2. Sa se proiecteze o masina cu stari finite care afiseaza urmatoarea secventa : 3,7,2,6,3,7,2 6 ...

Secventa de numarare va incepe cand se va apasa tasta ‘C’ si se va opri cand tasta nu mai este apasata. Se presupune ca stare urmatoare a starilor neutilizate este starea initiala a secventei. In cazul nostru : starea 3.

Problema numarul 1 :

Date de proiectare : Modulul digital va contine doar un semnal de intrare clk si la iesire un semnal pe patru biti numit digit.

Modalitati de proiectare : Numaratoarele se pot realiza cu ajutorul bistabilelor si a portilor logice, cele din urma având rolul de a stabili modul corect în care numaratorul îsi schimba starile în

procesul de numarare.

Entitatea numaratorului ce trebuie realizat :

Descrierea numaratorului este de tip comportamental prin specificatii secventiale în cadrul unui proces. Procesul este activat numai de catre semnalul clk. În zona declarativa a procesului este declarata o variabila temporara, temp, care realizeaza numararea efectiva.

In program nu vom avea intrarea ‘reset’ si nici nu vom initializa valoare variabilei temp de la inceput, ceea ce inseamna ca valoarea initiala a variabilei in circuitul fizic va fi orice valoare pe 4 biti. Daca valoarea aceasta este mai mica decat 10 programul va numara corect incepand cu acea valoare. Daca valoarea este mai mare decat 10 un numar de cicluri clk va fi repetat pana cand se ajunge la cel mai mare numar pe 4 biti, astfel fiind resetat automat la 0.

In program vom incrementa variabila temp si vom verifica mereu daca acesta a ajuns la valoarea 10. In momentul in care variabila temp a ajuns la valoarea 10 va fi resetata la 0.

Numararea se realizeaza pe frontul crescator a semnalului de ceas prin linia de cod: IF (clk'event AND clk='1')THEN.

Atribuirea semnalului de iesire se face la iesirea din proces. Acest lucru este indicat pentru ca semnalele sunt actualizate numai la iesirea din proces.

Listingul programului :

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity digitCounter is

port(

clk : in STD_LOGIC;

digit : out INTEGER range 0 to 9

);

end digitCounter;

architecture descriere of digitCounter is

begin

count: PROCESS(clk)

VARIABLE temp : INTEGER RANGE 0 TO 10;

BEGIN

IF (clk'EVENT AND clk='1') THEN

temp := temp + 1;

IF (temp=10) THEN temp := 0;

END IF;

END IF;

digit <= temp;

END PROCESS count;

end descriere;

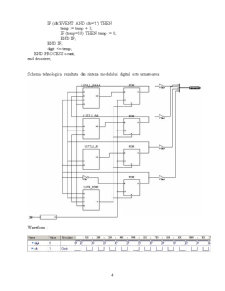

Schema tehnologica rezultata din sinteza modulului digital este urmatoarea:

Preview document

Conținut arhivă zip

- Sisteme Cad-Case.doc